## Part II. Functional Polymers for Semiconductor Applications

#### Outline of Part

- Introduction

- Basics for Semiconductor Theory

- Basics for Semiconductor Process

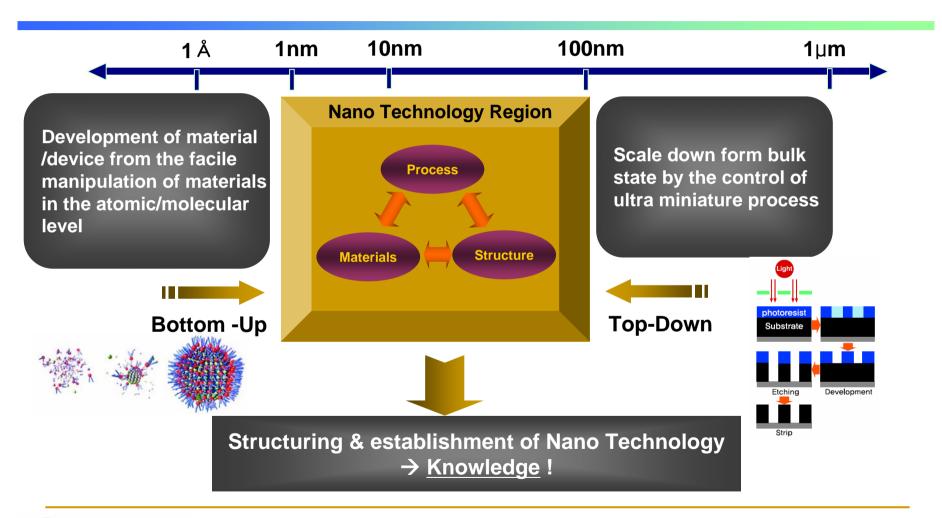

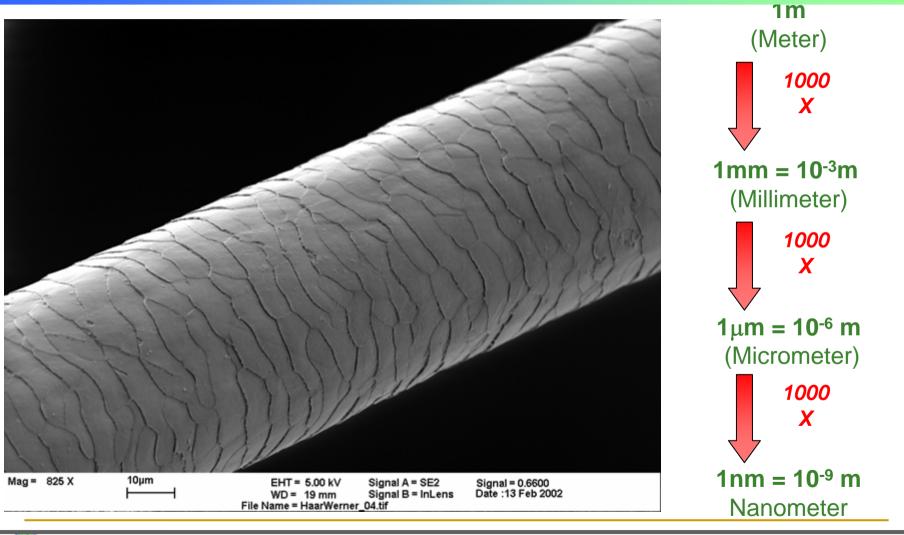

## Nano Technology

## Nano Technology

- •The creation of functional materials, devices and systems through control of matter at the scale of 1 to 100 nm, and the exploitation of novel properties and phenomena at the same scale.

- •Self-assembling highly functional molecular machines aimed at performing specific tasks. Often highly ordered repeated patterns of a single functional unit.

- $\bullet 1 \text{ nm} = 0.0000000001 \text{ m or } 0.00000001 \text{ mm } !!!!$

### **Nano Patterned Structure**

Biological molecules

Forms of carbon

Diamond

Weak bonding between layers

Graphite

Crystal structures

## **ITRS** Roadmap

#### 2002 ITRS Roadmap

| Year of Production                                                                | 2001    | 2002    | 2003    | 2004    | 2005    | 2006    | 2007    | 2010 | 2013 | 2016 |

|-----------------------------------------------------------------------------------|---------|---------|---------|---------|---------|---------|---------|------|------|------|

| MPU 1/2 Metal One Pitch<br>(nm)                                                   | 150     | 130     | 107     | 90      | 80      | 70      | 65      | 45   | 32   | 22   |

| Interlevel metal insulator<br>(minimum expected) —bulk<br>dielectric constant (k) | <2.7    | <2.7    | <2.7    | <2.4    | <2.4    | <2.4    | <2.1    | <1.9 | <1.7 | <1.6 |

| Interlevel metal insulator -<br>effective dielectric constant<br>(k)              | 3.0-3.6 | 3.0–3.6 | 3.0-3.6 | 2.6-3.1 | 2.6-3.1 | 2.6-3.1 | 2.3–2.7 | 2.1  | 1.9  | 1.8  |

Dense OSG Dense Organic

1st use at 130nm Not as easy as expected Not widely implemented until 90nm

Many users will want to extend to 65nm node Porous hybrid/OSG Porous organics CVD OSG

Many material candidates

Many new problems encountered

pore sealing, lower mechanical

strength, etc.

Some consider the roadmap unrealistic

Porous hybrid/ OSG

Porous organics

Structured porous OSG

CVD OSG?

CVD organic?

Most current materials are extensions of k > 2.2 versions

Outlook for k ~ 2.0 uncertain

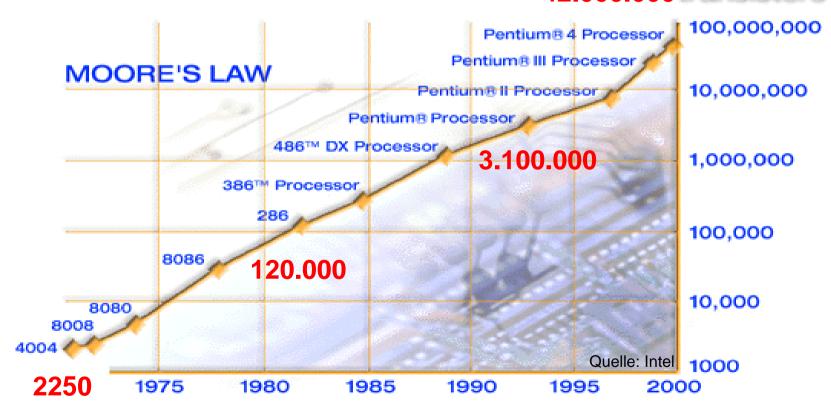

#### Moore's Law

#### 42.000.000transistors

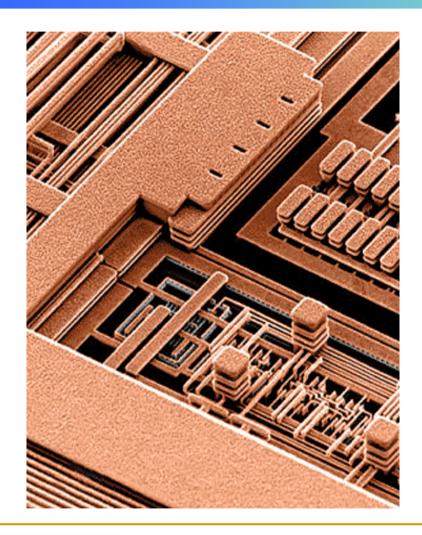

## 반도체 Chip I

## 반도체 Chip II

#### Nanometer Scale

## Small !!

## **Viewpoint of Nano Materials**

#### **Design & Synthesis**

- **■** Functional polymers

- Organic/inorganic hybrid Materia

- Nanoporous materials

- Nano dot, wire

#### **Process Technology**

- **■** Miniature process control (Top-down)

- Atom/Molecule control (Bottom-up)

- Characterization Technique

#### **Applications**

- **■** Electronics

- Energy/Catalyst

- Display

## Nano patterning

Transferring geometrical shapes and patterns on a mask to the surface of a silicon wafer.

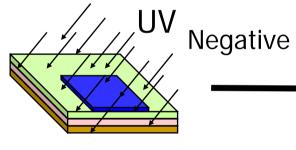

## Type of Photoresist (PR)

Positive photoresist

Light causes photoresist to become more "soluble" in the developer

The mask contains an exact copy of the pattern which is to remain on the wafer.

Negative photoresist

Remove mask

UV "polymerization"

Mask contains the "inverse" of the pattern to be transferred.

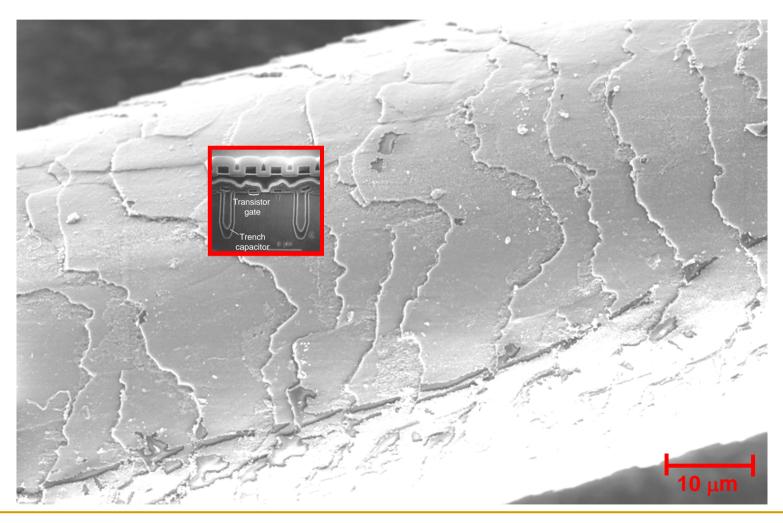

## **Real Semiconductor Device**

# Basics for Semiconductor Theory

### Silicon Lattice

- Transistors are built on a silicon substrate

- Silicon is a Group IV material

- Forms crystal lattice with bonds to four neighbors

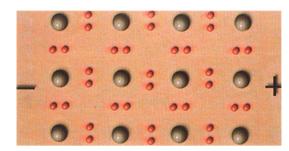

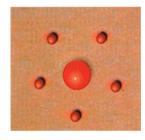

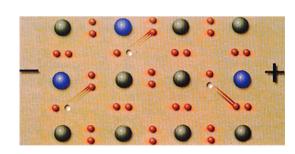

## **Dopants**

- Silicon is a semiconductor

- Pure silicon has no free carriers and conducts poorly

- Adding dopants increases the conductivity

- Group V: extra electron (n-type)

- Group III: missing electron, called hole (p-type)

## Semiconductor

🦲 Si: IV 족

As: V 족

B: III 족

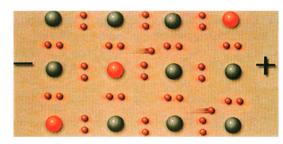

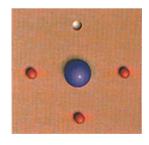

## p-n Junctions

- A junction between p-type and n-type semiconductor forms a diode.

- Current flows only in one direction

p-type n-type

anode cathode

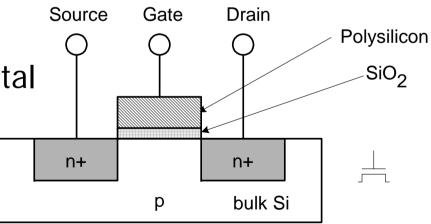

#### nMOS Transistor

- Four terminals: gate, source, drain, body

- Gate oxide body stack looks like a capacitor

- Gate and body are conductors

- SiO<sub>2</sub> (oxide) is a very good insulator

- Called metal oxide semiconductor (MOS) capacitor

- Even though gate is no longer made of metal

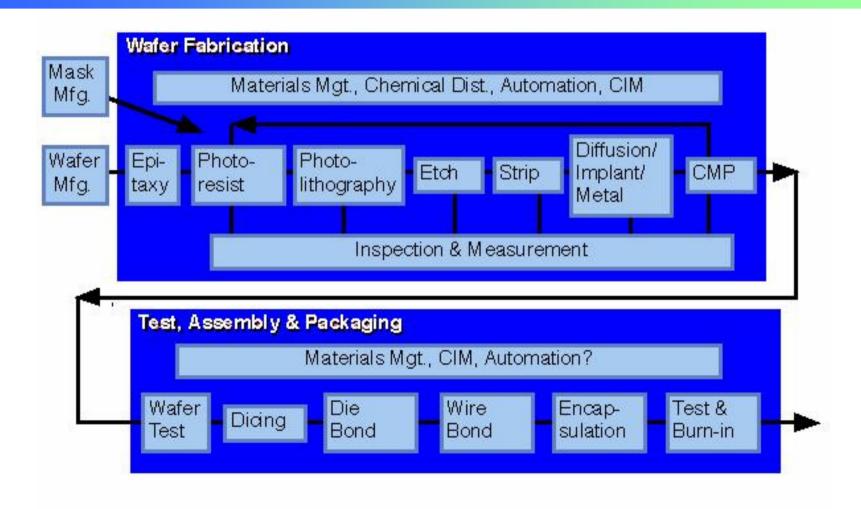

# Basics for Semiconductor Process

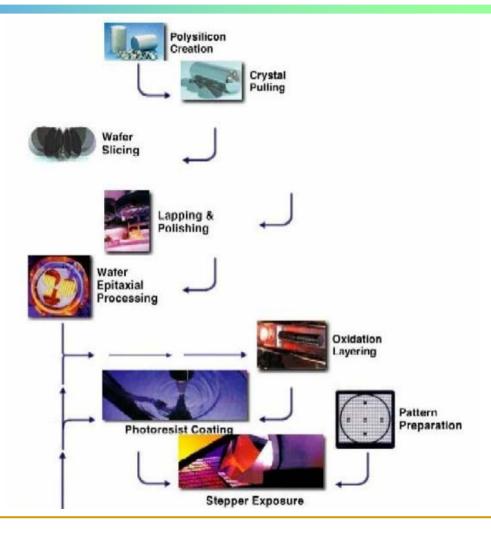

## 반도체 제조 공정

## 반도체 제조 공정 1

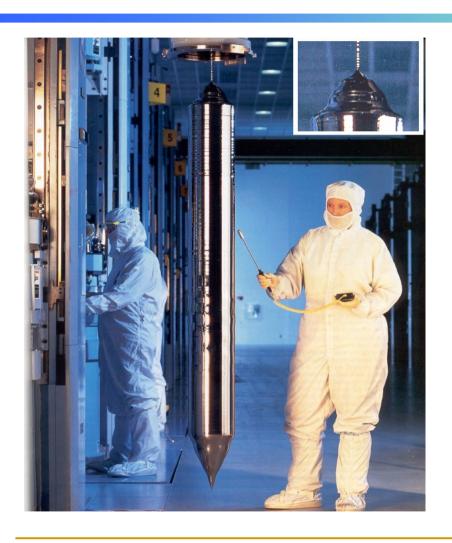

#### 1. Silicon Manufacturing

- a) Czochralski method.

- b) Wafer Manufacturing

- c) Crystal structure

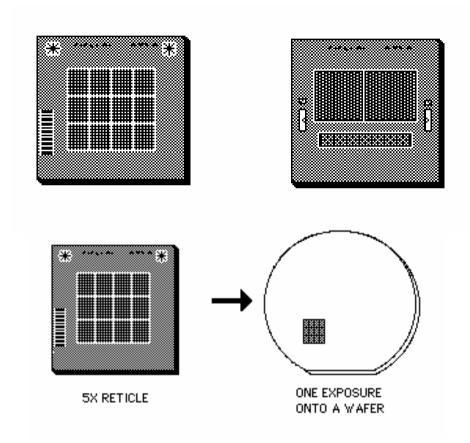

#### 2.Photolithography

- a) Photoresists

- b) Photomask and Reticles

- c) Patterning

## 반도체 제조 공정 1

#### 3. Oxide Growth & Removal

- a) Oxide Growth & Deposition

- b) Oxide Removal

- c) Other effects

- d) Local Oxidation

## 4. Diffusion & Ion Implantation

- a) Diffusion

- b) Other effects

- c) Ion Implantation

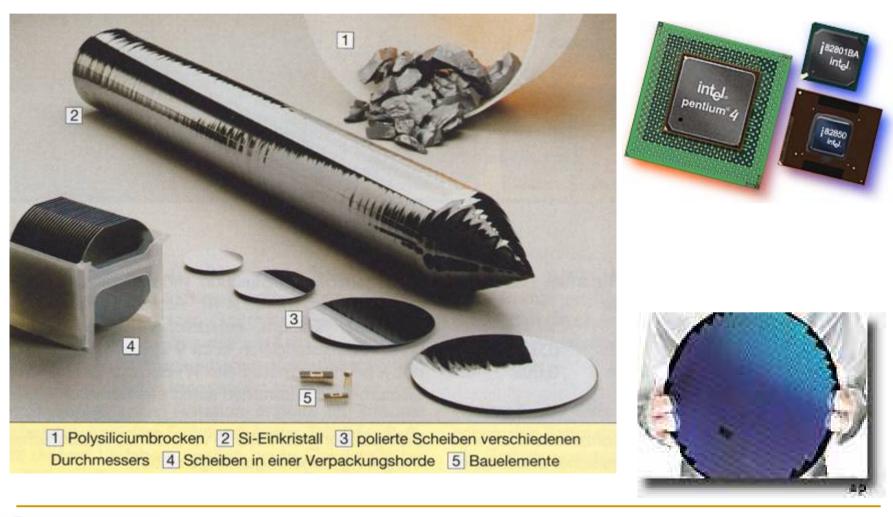

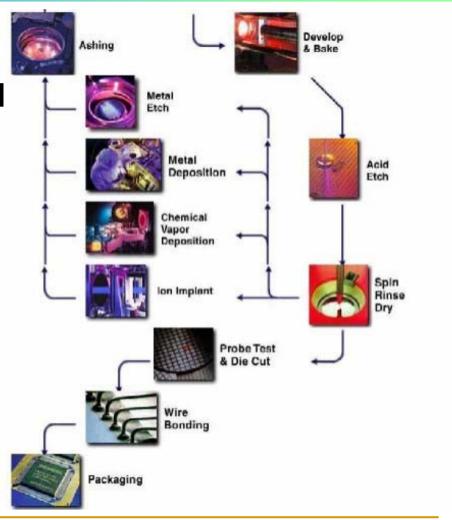

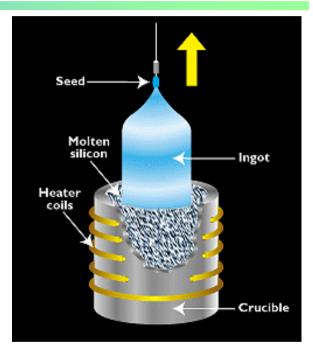

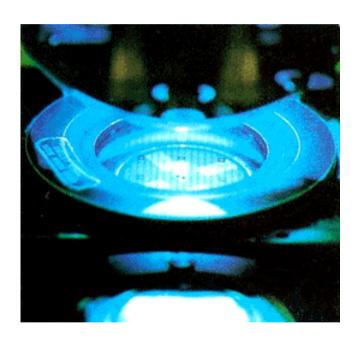

# Crystal Growth and Wafer Manufacturing

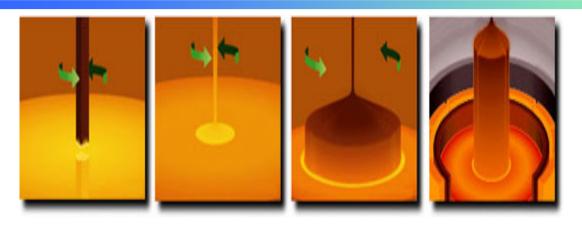

- Czochralski Process is a Technique in Making Single-Crystal Silicon

- A Solid Seed Crystal is Rotated and Slowly Extracted from a Pool of Molten Si

- Requires Careful Control to Give Crystals

Desired Purity and Dimensions

#### CYLINDER OF MONOCRYSTALLINE

- The Silicon Cylinder is Known as an Ingot

- Typical Ingot is About 1 or 2 Meters in Length

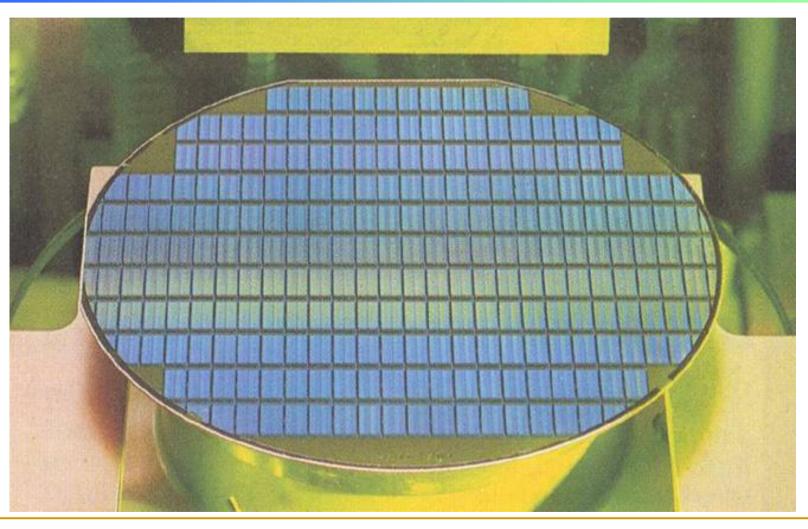

- Can be Sliced into Hundreds of Smaller Circular Pieces Called Wafers

- Each Wafer Yields Hundreds or Thousands of Integrated Circuits

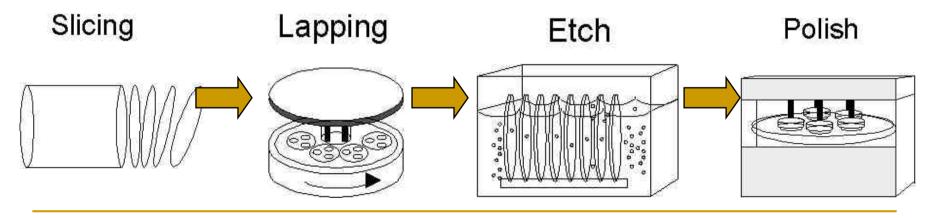

#### WAFER MANUFACTURING

- The Silicon Crystal is Sliced by Using a Diamond-Tipped Saw into Thin Wafers

- Sorted by Thickness

- Damaged Wafers Removed During Lapping

- Etch Wafers in Chemical to Remove any Remaining Crystal Damage

- Polishing Smoothes Uneven Surface Left by Sawing Process

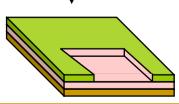

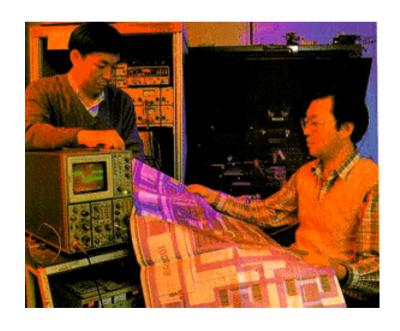

## **Architecture of Chips**

반도체 집적회로 중에서 모놀리식(monolithic)집적회로는 실리 콘 단결정 기판을 재료로 하여 한 개의 칩으로 구성한 것으로, 제작 공정은 필요한 부품을 배치, 회로를 구성하고, 이를 확대하여 제도한다. 확대된 모습, 설계하는 모습

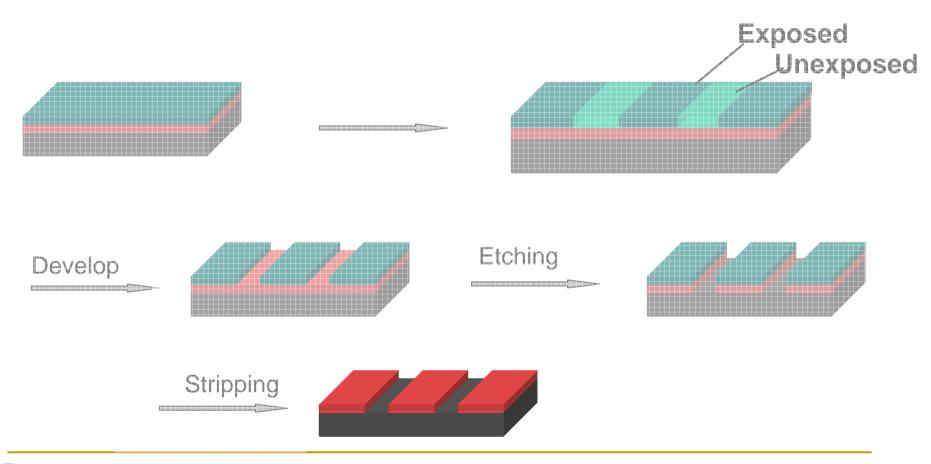

### **Fabrication Process I**

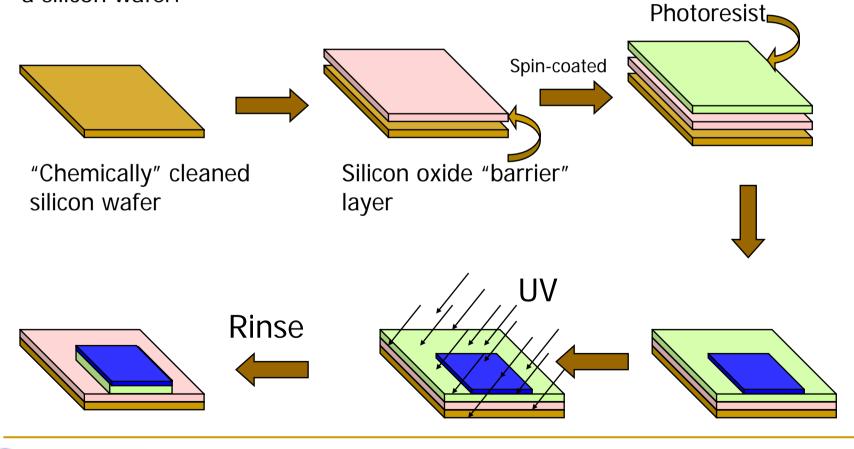

Photolithography is a technique that is used to define the shape of micromachined structures on a wafer.

- 감광액(Photo Resistor) 도포

- •노광(Exposure)

- •현상(Development)

- •식각(Etching), P/R 제거

## **Fabrication Process II**

라. 소자의 전기 특성 조절을 위해 불순물을 주입. 확산 열처리한다. (전기로 온도 1100도)

- •산화공정(Oxidation)

- •확산공정(Diffusion)

- •이온주입(Ion implantation)

- •화학 기상증착(CVD/LPCVD))

마. 내부 회로 연결을 위해 알루미늄 또는 금을 진공 증착한다 ; 금속배선(Metalization)

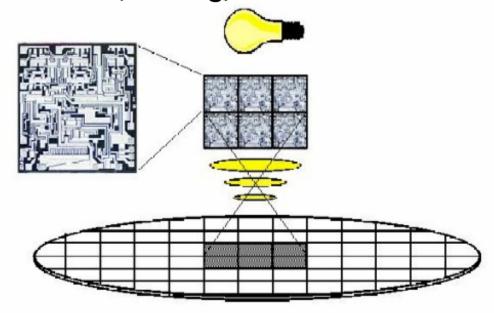

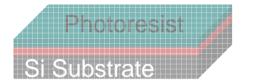

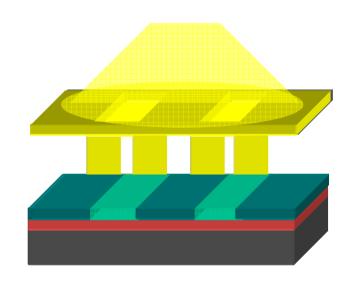

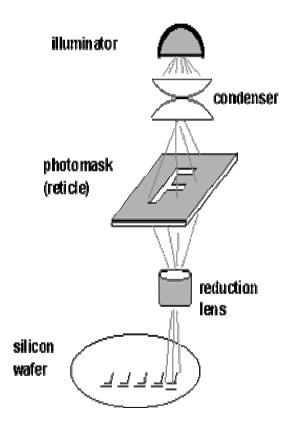

## Photolithography

- •The first step in the photolithography process is to develop a mask, which will be typically be a chromium pattern on a glass plate.

- •Next, the wafer is then coated with a polymer which is sensitive to ultraviolet light called a <u>photoresist</u>.

- Afterward, the photoresist is then developed which transfers the pattern on the mask to the photoresist layer.

## **Photo Patterning Process**

**Photoresist**

Si Substrate

Lithography: Photolithographie:

Photoresist:

일정하게 원하는 모양으로 깍는다.

빛을 이용하여 일정하게 원하는 모양으로 깍는다.

Material, 빛에 감응하는 물질

## **Photo Patterning Process I**

## **Photo Patterning Process II**

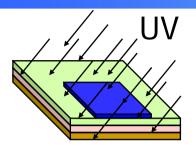

## **Photolithography Photoresist**

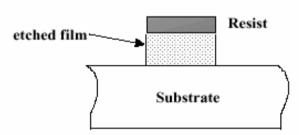

- Figure 1a shows a thin film of some material (eg, silicon dioxide) on a substrate of some other material (eg, a silicon wafer).

- Photoresist layer (Figure 1b )

- Ultraviolet light is then shone through the mask onto the photoresist (figure 1c).

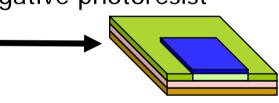

## **Photolithography Photoresist**

- The photoresist is then developed which transfers the pattern on the mask to the photoresist layer (figure 1d).

- A chemical (or some other method) is then used to remove the oxide where it is exposed through the openings in the resist (figure 1e).

- Finally the resist is removed leaving the patterned oxide (figure 1f).

### **Photomask**

#### **Examples of Photomask**

### **Oxidation of Silicon**

The simplest method of producing an oxide layer consists of heating a silicon wafer in an oxidizing atmosphere.

Heat wafers in an atmosphere containing an oxidant, usually O<sub>2</sub>, steam, or N<sub>2</sub>O.

$$\begin{split} Si + O_2 &\rightarrow SiO_2 \\ Si + 2H_2O &\rightarrow SiO_2 + 2H_2 \\ Si + 2N_2O &\rightarrow SiO_2 + 2N_2 \end{split}$$

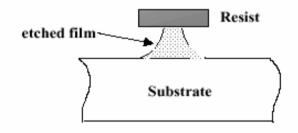

# **Etching Process**

Etching is the process where unwanted areas of films are removed by either dissolving them in a wet chemical solution (**Wet Etching**) or by reacting them with gases in a plasma to form volatile products (**Dry Etching**).

Resist protects areas which are to remain. In some cases a hard mask, usually patterned layers of  $SiO_2$  or  $Si_3N_4$ , are used when the etch selectivity to photoresist is low or the etching environment causes resist to delaminate. This is part of lithography - pattern transfer.

# **Etching Process**

### **Terminology**

- · Isotropic etch

- a process that etches at the same rate in all directions.

- Anisotropic etch

- a process that etches only in one direction.

# **Wet Chemical Etching**

#### Wet etches:

- are in general isotropic

(not used to etch features less than ≈ 3 µm)

- achieve high selectivities for most film combinations

- capable of high throughputs

- use comparably cheap equipment

- can have resist adhesion problems

- can etch just about anything

# **Wet Chemical Etching**

- For SiO<sub>2</sub> etching

- HF + NH<sub>4</sub>F+H<sub>2</sub>O (buffered oxide etch or BOE)

- For Si<sub>3</sub>N<sub>4</sub>

- Hot phosphoric acid: H<sub>3</sub>PO<sub>4</sub> at 180 °C

- need to use oxide hard mask

- Silicon

- Nitric, HF, acetic acids

- $HNO_3$  + HF +  $CH_3COOH$  +  $H_2O$

- Aluminum

- Acetic, nitric, phosphoric acids at 35-45 °C

- CH<sub>3</sub>COOH+HNO<sub>3</sub>+H<sub>3</sub>PO<sub>4</sub>

### What is a plasma?

- A plasma is a partially ionized gas made up of equal parts positively and negatively charged particles.

- Plasmas are generated by flowing gases through an electric or magnetic field.

- These fields remove electrons from some of the gas molecules. The liberated electrons are accelerated, or energized, by the fields.

- The energetic electrons slam into other gas molecules, liberating more electrons, which are accelerated and liberate more electrons from gas molecules, thus sustaining the plasma.

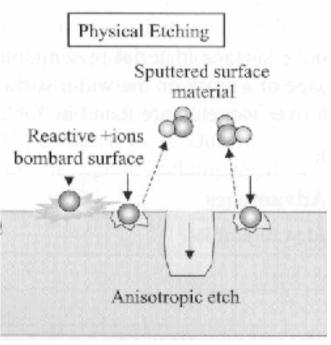

### **Dry or Plasma Process**

- Three different mechanisms

- Purely physical (sputtering)

- Can be anisotropic

- All materials have sputter yields within a factor of about 3, therefore <u>selectivities</u> will be low

- nonvolatile species can redeposit on surfaces

- ex. Ion Milling process

Semiconductor Manufacturing Technology, Quirk and Serda, Prentice Hall, 2001

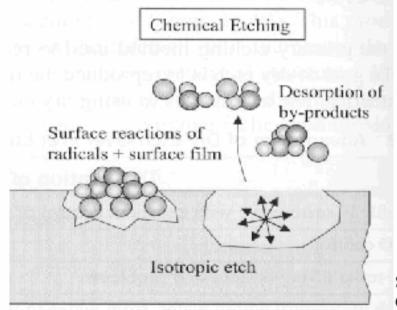

### **Dry or Plasma Process**

- Purely chemical

- isotropic

- · can have high selectivities

- · similar to wet etching

- ex. High Pressure Plasma process

Semiconductor Manufacturing Technology, Quirk and Serda, Prentice Hall,2001

## **Dry or Plasma Process**

# Combination of chemical and physical etching – Reactive Ion Etching (RIE)

Directional etching due to ion assistance.

In RIE processes the wafers sit on the powered electrode. This placement sets up a negative bias on the wafer which accelerates positively charge ions toward the surface. These ions enhance the chemical etching mechanisms and allow **anisotropic** etching.

Wet etches are simpler, but dry etches provide better line width control since it is anisotropic.

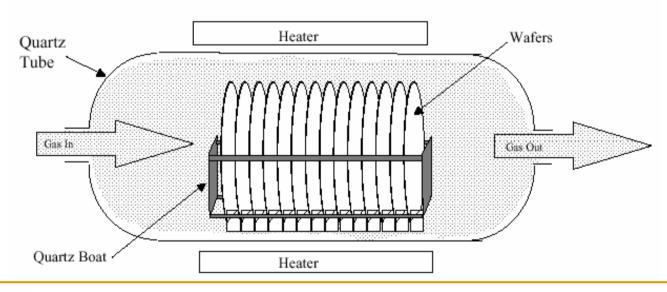

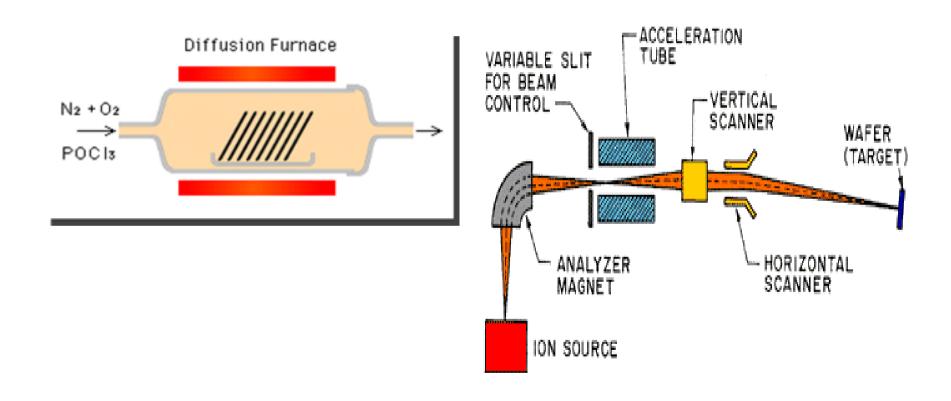

## Diffusion and Ion Implantation

#### Diffusion

- A uniformly doped ingot is sliced into wafers.

- An oxide film is then grown on the wafers.

- The film is patterned and etched using photolithography exposing specific sections of the silicon.

- The wafers are then spun with an opposite polarity doping source adhering only to the exposed areas.

- The wafers are then heated in a furnace (800-1250 deg.C) to drive the doping atoms into the silicon.

#### Ion Implantation

- A particle accelerator is used to accelerate a doping atom so that it can penetrate a silicon crystal to a depth of several microns

- Lattice damage to the crystal is then repaired by heating the wafer at a moderate temperature for a few minutes. This process is called annealing.

# Diffusion and Ion Implantation

# Inspection

■ 바. 웨이퍼내에 완성된 각 소자의 전기기능을 컴퓨터로 검사 선별한다.

; 웨이퍼 자동 선별(Testing & Sorting)

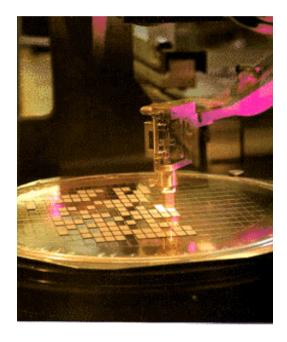

### **Chip Cutting**

사. 웨이퍼내의 칩을 다이아몬드 절단기로 분리한다.: 웨이퍼 절단(Sieving)

• 칩 접착(Die Bonding): 낱개로 분리된 칩 가운데 제대로 작동하는 것만을 Lead Frame위에 골라내어 올려놓는다. 리드 프레임이란 반도체에서 지네발처럼 튀어나온 다리 부분인데 반도체가 전자 제품에 연결되는 소켓의 구실을 한다. 불량으로 판정된 제품은 자동으로 제외된다.

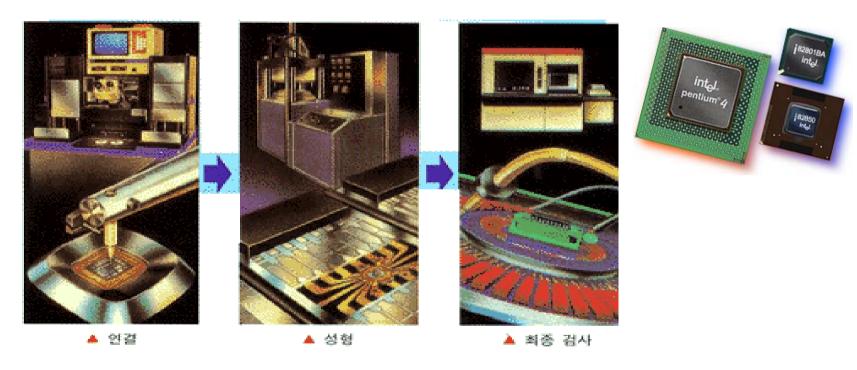

### Device 완성

- 자. 알루미늄, 금선을 이용하여 칩의 전극과 리드프레임의 단자를 연결한다.

- 차. 칩, 리드프레임으로 된 내부 소자를 프라스틱 성형한다.

- 카. 완제품

#### ■ 반도체 제조공정

반도체 제조 과정을 크게 3단계로 나누어진다. 첫번째는 **웨이퍼 제조 및 회로 설계**, 두번째는 **웨이퍼 가공**, 마지막으로 <u>조립 및 검사</u>들이다. 하지만 작게 분류해 보면 3백 단계가 넘는 무수히 복잡한 공정을 거쳐 비로소 한개의 반도 체가 탄생한다는 것을 알 수 있다.

#### √ 웨이퍼 제조 및 회로 설계

- ⓐ **단결정 성장** : 고순도로 정제된 실리콘 (규소) 용액을 주물에 넣어 회전시키면서 실리콘 기둥(봉)을 만든다.

- (b) 실리콘 봉 절단: 규소 기둥을 똑같은 두께의 얇은 웨이퍼로 잘라낸다. 반도체 공장 사진을 보면, 작업자가 손바닥만한 둥근 거울 같은 것을 들고 있는 장면을 자주 보는데 이 둥근 거울 같은 것이 웨이퍼다. 반도체는 이 웨이퍼에 회로를 만들어 손톱만한 크기로 잘라 만드는 것이다.

- ⓒ 웨이퍼 표면 안마: 웨이퍼의 한쪽 면을 닦아 거울처럼 반질거리게 만들어 준다. 이 연마된 표면에 전자 회로의 패턴을 그려 넣게 된다.

- ⓓ **회로 설계**: 컴퓨터 시스템을 이용해 전자회로 패턴을 설계한다. 보통 반도체의 회로도 면은 50∼100미터 정도의 크기다.

- ② 마스크 제작: 설계된 회로 패턴을 유리판 위에 그린다. 이것이 마스크다. 포토 마스크라고도 하는데 사진용 원판의 구실을 한다. 현상 공정에서 마스크를 웨이퍼 위에 얹은 다음 강한 자외선을 비추면 유리 위에 그려진 회로가 웨이퍼에도 똑같이 그려진다. 사진의 현상과 비슷한 원리다.

#### ✔ 웨이퍼 가공

- ① 반도체 제조 회사라고 하면 일반적으로 웨이퍼 가공부터 시작하는 회사를 일컫는다. 웨이퍼 생산은 전문업체들의 몫이다.

- ⑨ 산화 (Oxidation) 공정: 고온 (800~1200도) 에서 산소나 수증기를 실리콘 웨이퍼 표면에 뿌려 산화막을 형성시킨다. 산화막은 웨이퍼 위에 그려질 배선끼리 합선되지 않도록 서로를 구분해 준다. 배선간의 간격이 미세하기 때문에 합선이 될 경우가 많다.

- 확산(Diffusion)공정: 고온(1000~1200도)에서 Silicon 안으로 n(donor)- or p(acceptor)-type impurities를 확산시켜 n-or p-영역을 형성하는 공정

- (h) **감광액 도포**: 감광액을 웨이퍼 표면에 고르게 바른다. 그 다음 이를 살짝 구워서 얼라이 너 (Aligner)라고 불리는 사진 촬영장치로 보낸다. 이때부터 웨이퍼는 사진의 인화지 역할을 하다.

- ① 노광 (Exposure): 포토 마스크를 웨이퍼 위에 얹은 다음, 조준을 맞추고 강한 자외선을 통과시킨다. 자외선 빛은 마스크 위의 회로 패턴을 웨이퍼에 그려준다.

- ① **현상** (Development): 일반 사진 현상과 동일하다. 현상액을 웨이퍼에 뿌리면 웨이퍼는 노광 과정에서 빛을 받은 부분과 받지 않은 부분으로 구분되는데, 빛을 받은 부분의 현상액은 날아가고 빛을 받지 않은 부분은 그대로 남는다.(for Positive P/R)

- ⓒ 식각 (Etching): 웨이퍼에 회로 패턴을 만들어 주기 위해 화공약품 (습식) 이나 부식성 가스 (건식)을 이용해 필요 없는 부분을 선택적으로 없앤다. 현상액이 남아있는 부분을 남겨둔채 나머지 부분은 부식시킨다. 식각이 끝나면 감광액도 황산용액으로 제거한다. 이 과정은 동판화를 만드는 것과 다를 바 없다. 동판화 제작 과정을 보자. 동판 위에 파라핀을 바르고 (반도체의 감광액) 표면을 불로 그을린 뒤 (반도체의 산화 공정) 그 위에 날카로운 송곳 같은 것으로 그림을 그린다. 송곳이 지나간 자리에는 파라핀이 벗겨진다. 그 다음 부식시키는 화공약품을 붓는다 (반도체의 식각). 화공약품과 파라핀을 씻어내면 그림이 완성된다. 이런 과정은 반도체도 동판제작과 다를 바가 없다.

- ① **이온 주입 (lon Implantation)**: n- or p-type 불순물을 에너지를 가진 미세한 가스 입자형태로 Slicon 안으로 강제 주입시켜 n-or p-영역을 형성하여 전기 소자의 특성을 만들어준다.

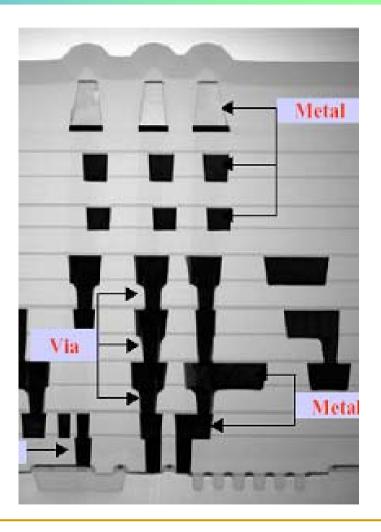

- ⑩ **화학 기상 증착 (Chemical Vapor Deposition)**: 가스의 화학반응으로 형성된 입자들을 웨이퍼 표면에 수증기 형태로 쏘아 (증착) 절연막이나 전도성막을 형성시킨다. 일종의 보호 막과도 같은 역할을 한다.

- ① 금속배선 증착: 웨이퍼 표면에 형성된 각각의 회로를 금,은,알루미늄 선으로 연결시키는 공정. 금속에 열을 가하거나 전기적 충격을 주면 금속이 기화되어 증발하여 wafer에 증착된다. 증착된 metal layer를 mask를 사용하여 회로배선에 필요한 부분을 제외하고 시각하면 회로가 형성된다. Process로는 Evaporation 과 Sputtering 방법이 있다.

- 조립 및 검사

- ⑨ 웨이퍼 자동 선별(Sorting): 칩들의 불량 여부를 컴퓨터로 검사하여 불량품을 골라낸다.

불량제품은 검은 잉크로 동그란 마크를 찍어 분류한다.

- P 웨이퍼 절단(Sieving): 웨이퍼에 그려진 하나하나의 칩들을 떼어내기 위해 웨이퍼를 손톱만한 크기로 계속 잘라낸다. 절단에는 다이아몬드 톱이 사용된다.

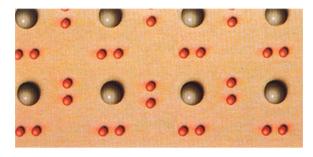

- ⑨ 칩 접착(Die Bonding): 낱개로 분리된 칩 가운데 제대로 작동하는 것만을 골라내어 리드 프레임 위에 올려놓는다. 리드 프레임 (Red Frame) 이란 반도체에서 지네발처럼 튀어나온 다리 부분인데 반도체가 전자 제품에 연결되는 소켓의 구실을 한다. 불량으로 판정된 제품은 자동으로 제외된다.

- ① 금(金) 선 연결(Wire Bonding): 칩의 외부 연결 단자와 리드 프레임을 가느다란 금선으로 연결해 준다. 머리카락보다 가는 순금을 사용한다. 이 장면은 TV에 가끔씩 나온다. 네모난 금속성 칩이 있고, 그 주위를 작은 막대기 같은 것이 나와서 바쁘게 선을 연결하는 장면이다.

- ⑤ 성형 (Molding): 외형 만들기 작업이다. 이 과정을 거쳐 우리가 흔히 볼 수 있는 검은색지네발 모양이 된다. 칩과 연결 금선을 보호해 주기 위해 화학수지로 밀봉해 준다. 플라스틱이나 세라믹 같은 것으로 감싸준다. 그 다음 윗면에 제품명이나 고유 번호, 제조회사의마크 등을 인쇄한다.

- ① 최종 검사: 완성된 반도체의 전기적 특성이나 기능 등을 컴퓨터로 최종 검사한다. 강제로 높은 정전기를 흘린 다음 제품이 제대로 작동하는지, 높거나 낮은 습도에서, 높은 온도에서 잘 견디는지 등을 확인한다. 합격된 제품은 판매한다.

- 웨이퍼 가공에서 완제품까지는 최소한 한달 보름 이상이 걸린다. 지금 막 라인에서 쏟아져 나오는 반도체는 적어도 한달 반 이전에 제작되기 시작한 것이다.